Reti logiche/Componenti

Reti logiche

[modifica | modifica sorgente]Una rete logica è un insieme di dispositivi interconnessi che realizza un'elaborazione. Possono essere di natura elettronica, nell'accezione più comune, ma potenzialmente anche di altra natura, se in grado di trasmettere e elaborare un segnale, come nella fotonica, eccetera. Esistono essenzialmente due tipi principali di reti logiche, le reti unilaterali e le reti bilaterali.

Le reti unilaterali sono reti in cui lo stato delle uscite, cioè se l'uscita assume valore alto o basso, dipende esclusivamente da valori di grandezze elettriche calcolate in un determinato punto del circuito: in queste reti il flusso dell'elaborazione procede fisicamente in un'unica direzione e ne sono esempi elementari le porte logiche; per chiarire meglio, consideriamo una porta AND a due ingressi: lo stato dell'uscita della porta AND dipende dai valori di corrente applicati ai due pin di entrata e il flusso dell'elaborazione procede dai pin di entrata al pin di uscita.

Le reti bilaterali sono reti in cui la funzione di uscita è valutata tra due punti, cioè l'uscita è determinata dal fatto che ci sia o meno un contatto tra due punti: se ad esempio nel punto A arriva corrente ma non c'è contatto con B allora l'uscita sarà bassa, se c'è contatto l'uscita sarà alta; inoltre non è detto che la corrente possa scorrere solo da A verso B, ma anche da B verso A, a differenza delle reti unilaterali.

Gli esempi fatti sui due tipi di reti sono banali ma più in generale si possono avere reti logiche unilaterali quali i circuiti combinatori o i circuiti sequenziali che sono circuiti fatti di porte logiche (reti unilaterali elementari) e poi abbiamo i circuiti fatti da elementi quali resistori, condensatori o induttori collegati in serie e/o parallelo per formare circuiti più complessi.

Il nome rete logica è di norma associato solo a reti che eseguono un'elaborazione elettronica quali i circuiti combinatori e sequenziali in quanto elaborano dei dati secondo logica, cioè secondo la logica prevista dal progetto della rete; si tende invece a distinguere da queste reti i circuiti elettrici che hanno altre funzioni.

Logica combinatoria di base

[modifica | modifica sorgente]Nella teoria dei circuiti digitali la logica combinatoria è un tipo di circuito logico che si chiama circuito combinatorio e il cui funzionamento riguarda solo la relazione ingresso-uscita, e tale relazione è descritta da una funzione logica. I circuiti combinatori in particolare sono quelli in cui gli ingressi e le uscite possono assumere solo due stati corrispondenti ai livelli alto o basso, e le uscite sono funzione unicamente degli ingressi. Per tale motivo sono anche chiamati circuiti senza memoria, le uscite in ogni istante sono funzione esclusivamente dei valori degli ingressi in quello stesso istante.

Nei circuiti combinatori una funzione logica degli ingressi si realizza attraverso componenti capaci di assumere uno dei due stati di tensione: il livello alto e il livello basso, indicati rispettivamente con h e l.

In un circuito combinatorio si può lavorare in logica positiva, cioè la convenzione secondo la quale il valore logico 1 viene associato al livello alto e di conseguenza il valore logico 0 viene associato al livello basso. In alternativa si può lavorare in logica negativa, secondo la convenzione che al valore logico 1 si associa al livello di tensione basso e di conseguenza il valore logico 0 si associa al livello di tensione alto. Le reti logiche combinatorie sono quelle reti in cui lo stato d'uscita viene a dipendere solo ed esclusivamente dallo stato degli ingressi propri presenti in quell'istante.

Analisi e Sintesi

[modifica | modifica sorgente]Si pone il problema di ottimizzare i circuiti combinatori. I criteri di ottimizzazione possono essere diversi a seconda dei problemi per esempio, ottimizzazione dei costi, ottimizzazione della funzionalità, o della velocità, o nella maggior parte dei casi si cerca una via ponderata per tutte queste esigenze. In particolare il costo di un circuito logico è caratterizzato dal numero di porte logiche utilizzate, dalla profondità, cioè dalla lunghezza del percorso tra l'input e l'output, che tiene conto dei ritardi temporali e dal numero di ingressi.

In questo contesto la sintesi di un circuito combinatorio o rete combinatoria è l'individuazione, una volta assegnata la specifica funzionale del circuito, del sistema digitale e le interconnessione che realizzano tale specifica.

Per analisi di un circuito combinatorio, si intende l'individuazione delle relazioni causa-effetto tra i segnali di ingresso, cioè le variabili booleane in ingresso, e le uscite del circuito.

Per svolgere questi compiti si utilizza l'algebra di Boole.

In generale una rete logica combinatoria viene progettata partendo da una descrizione funzionale della rete logica, cioè quello che deve fare. A partire dall'algebra di Boole, si rappresenta la rete logica con una funzione logica, una tabella della verità o con una mappa di Karnaugh. Poi entra in gioco la riduzione della funzione in forma minima, per ottimizzare la rete logica e infine si passa alla realizzazione effettiva circuitale.

In realtà, la progettazione è praticamente un problema di sintesi, ma nel quale poi si devono considerare i problemi di alee.

Circuito porta

[modifica | modifica sorgente]Si chiama circuito porta il circuito elementare che possiede n ingressi ed un'unica uscita, il cui valore logico di uscita è 1 oppure 0 a seconda della descrizione logica degli operatori logici: AND, OR, NOT, NOR, NAND, e così via. Per ogni tipo di circuiti si pone il problema dell'analisi, cioè della descrizione del funzionamento del circuito nota la sua configurazione e della sintesi, cioè della progettazione del circuito che realizza una certa funzione logica.

- congiunzione logica AND

L'operazione AND dà come valore 1 se tutti gli operandi hanno valore 1, mentre restituisce 0 in tutti gli altri casi come ad esempio quando una porta è alta mentre le altre sono basse e può essere messa in serie. Tale operazione è anche detta prodotto logico. Di seguito la tabella rappresenta l'operatore AND nel caso di due entrate, ma la definizione data ora è generalizzata a n ingressi:

| A | B | A AND B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Siccome questa operazione gode della proprietà associativa, è possibile realizzare un'operazione logica AND con un numero di proposizioni arbitrarie concatenando varie AND a due ingressi, per esempio:

Nei circuiti digitali, la porta logica AND è un meccanismo comune per avere un segnale di vero se un certo numero di altri segnali sono tutti veri.

Nella teoria degli insiemi corrisponde all'intersezione.

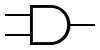

Il simbolo di una porta AND è:

- disgiunzione logica OR

L'operazione logica OR restituisce 1 se almeno uno degli elementi è 1, mentre restituisce 0 in tutti gli altri casi. Tale operazione è anche detta somma logica. Di seguito la tabella rappresenta l'operatore OR nel caso di due entrate, ma la definizione data ora è generalizzata a n ingressi:

| A | B | A OR B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Siccome questa operazione gode della proprietà associativa, è possibile realizzare un'operazione logica OR con più ingressi concatenando varie OR a due ingressi, per esempio:

Nei circuiti digitali, la porta logica OR è un meccanismo comune per avere un segnale alto se almeno un segnale è alto e un segnale basso se e solo se tutti i segnali sono bassi.

Nella teoria degli insiemi corrisponde all'unione.

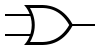

Il simbolo di una porta OR a due ingressi è:

- invertitore logico Not

Il not viene utilizzato in matematica allo scopo di negare un'affermazione: se A è la proposizione da contraddire, la scrittura dovrà essere ¬A; per quanto riguarda le tabelle di verità, dunque, la negazione è l'operatore più semplice ed intuitivo: se la proposizione A è vera, allora ¬A è falsa, e viceversa. Nella scrittura a mano è spesso preferito a questo simbolo un altro che al computer è quasi impossibile digitare: si tratta di un trattino posto al di sopra della proposizione da negare: dunque Ā = ¬A. Le immagini ingrandite dei due possibili segni sono visibili alla destra e alla sinistra di questa specifica voce. Data una proposizione p si ha che ¬p è falsa se p è vera, ed è vera se p è falsa. La w:tabella di veritàtabella di verità della negazione è la seguente:

| F | V |

| V | F |

- NAND negazione di AND

L'operatore NAND, la negazione del risultato dell'operazione AND, restituisce 0 se e solo se tutti gli elementi sono 1, mentre restituisce 1 in tutti gli altri casi.

| A | B | A NAND B |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

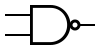

Il simbolo di una porta NAND è:

composta da un NOT in serie a un AND.

Utilizzando le leggi di De Morgan, è possibile convertire una porta OR in NAND. Vale, dunque, la seguente relazione:

- NOR negazione di OR

L'operatore NOR, la negazione del risultato dell'operazione OR, restituisce 1 se e solo se tutti gli elementi sono 0, mentre restituisce 0 in tutti gli altri casi.

| A | B | A NOR B |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Il simbolo di una porta NOR è:

composta da un NOT in serie a un OR.

Utilizzando le leggi di De Morgan, è possibile convertire una porta AND in NOR. Vale, dunque, la seguente relazione:

Logica sequenziale

[modifica | modifica sorgente]Nella teoria dei circuiti digitali, la logica sequenziale è un circuito logico in cui le uscite all'istante t non dipendono solo dagli ingressi nel medesimo istante, ma anche dai valori assunti in precedenza: si tratta ovvero di un sistema dinamico dotato di memoria.

In elettronica digitale il modello più generale di circuito è quello composto da n ingressi ed m uscite entrambi funzioni del tempo. Se in ogni istante il valore istantaneo delle uscite è determinato univocamente dai valori degli ingressi, il circuito è detto combinatorio, allora esso non dipende esplicitamente dal tempo. Quando invece il valore istantaneo delle uscite dipende anche dalla storia passata del circuito allora si parla appunto di circuito sequenziale.

Risulta allora necessario che le informazioni debbano essere memorizzate o registrate per essere poi utilizzate. L'elemento di memorizzazione elementare è il flip-flop, del quale ne esistono diversi tipi. Ma la cosa più importante per il funzionamento dei circuiti sequenziali è la temporizzazione, per diversi motivi: innanzitutto perché i circuiti sequenziali utilizzano macchine sequenziali, che sono per antonomasia le teorizzazioni dei dispositivi elettronici praticamente utilizzati: a tale scopo diciamo solo che una macchina sequenziale ha un numero di stati interni e una serie di regole che attraverso i valori degli ingressi e attraverso la mappa di transizione danno la mappa delle uscite, tutte quantità che dipendono dal tempo.

Componenti

[modifica | modifica sorgente]Componenti sequenziali standard

[modifica | modifica sorgente]Latch

[modifica | modifica sorgente]In elettronica digitale, il latch è un circuito elettronico bistabile, caratterizzato quindi da almeno due stati stabili, in grado di memorizzare un bit di informazione nei sistemi a logica sequenziale asincrona. Il latch modifica lo stato logico dell'uscita al variare del segnale di ingresso, mentre il flip-flop, basato sulla struttura del latch, cambia lo stato logico dell'uscita solamente quando il segnale di clock è nel semiperiodo attivo. Il latch costituisce l'elemento base di tutti i circuiti sequenziali ma trova anche delle applicazioni come elemento singolo, ad esempio per eliminare i rimbalzi dei componenti elettromeccanici come pulsanti, interruttori e commutatori.

Spesso i latch sono usati in gruppi, alcuni dei quali hanno nomi speciali come il quad latch (gruppo di quattro) e l'octal latch (gruppo di otto). Molti tipi di display a 7 segmenti o alfanumerici contenenti il circuito di decodifica, dispongono di un pin collegato a questo circuito, il quale permette tramite il cambio del livello logico, di "stoppare" il valore in quel momento visualizzato.

- Latch SR

Il latch più semplice (che permette di forzare uno stato dall'esterno) è il latch SR, dove S ed R stanno per Set (imposta) e Reset (reimposta). Questo tipo di latch è composto da due porte NAND (Not AND) o da due porte NOR (Not OR) con collegamenti incrociati, ottenendo rispettivamente la versione attiva bassa e la versione attiva alta, Il bit immagazzinato è portato all'uscita e il suo complemento all'uscita .

Nella versione attiva bassa, normalmente in modalità di immagazzinamento, gli input e vengono tenuti a livello logico alto così che il feedback mantenga gli output e in uno stato costante.

Quando viene abbassato il livello logico sull'input (set) l'output passa ad alto e resta alto anche quando torna alto. Al contrario, quando (reset) viene abbassato, l'output diventa basso e resta basso anche quando torna alto.

Se entrambi e vengono abbassati in concomitanza, l'output del latch è indeterminato, quindi questa condizione deve essere evitata.

In maniera duale, nella versione attiva alta, lo stato di memoria si ottiene quando entrambi gli ingressi sono bassi. La funzione di reset avviene quando è alto l'ingresso R e la funzione set quando è alto l'ingresso S. La condizione da evitare perché lo stato dell'uscita resta indeterminato è quella dei due ingressi entrambi alti.

Tabella della verità del Latch SR attivo basso:

| Funzione ------+----------- 0 0 | Non è ammesso 0 1 | Set: Q = 1 , !Q = 0 1 0 | Reset: Q=0 , !Q = 1 1 1 | Latch (Memorizzazione) |

Tabella della verità del Latch SR attivo alto:

| Funzione ------+----------- 0 0 | Latch (Memorizzazione) 0 1 | Reset: Q = 0 , !Q = 1 1 0 | Set: Q = 1 , !Q = 0 1 1 | Non è ammesso |

- Latch D

Il Latch di tipo D (delay/DL) è un circuito nel quale viene eliminata la condizione di indeterminazione tipica del latch SR. Per fare questo l'ingresso S viene portato all'esterno sotto il nome di D, mentre l'ingresso R non è accessibile all'esterno e riceve il segnale di S negato.

Questa soluzione elimina la possibilità che i due ingressi S ed R assumano valori uguali.

Nel latch D è presente, inoltre, un ingresso E (enable) che ha la funzione di abilitazione. Se l'ingresso E viene mantenuto a livello basso l'uscita conserva il proprio stato indipendentemente dal valore assunto dall'ingresso D in quell'istante. Se E viene portato a 1 l'uscita assume il valore che in quell'istante è presente sull'ingresso D. Allorché E torna a 0 l'uscita mantiene lo stato assunto e la situazione di memoria si mantiene fino a che E torna ad 1 con un valore di D diverso dal precedente.

Tabella della verità del latch D

E D | ------+----------- 1 0 | 0 1 1 1 | 1 0 0 - | |

La caratteristica di mantenimento dell'uscita da parte del latch D lo rende adatto all'impiego come interfaccia-memoria nel comando di tastiere o visualizzatori. Un limite al campo di applicazione di questo componente è dato dal fatto che esso è trasparente, in quanto lo stato dell'ingresso si porI flip-flop (o bistabili) sono circuiti elettronici sequenziali molto semplici, utilizzati nell'elettronica digitale come dispositivi di memoria elementare. Il nome Flip-Flop deriva dal rumore che facevano i primi circuiti di questo tipo, costruiti con relè che permettevano il cambiamento di stato.

Possono essere utilizzati anche come circuito anti-rimbalzo per i contatti di un pulsante, un interruttore o un relè, indispensabili per esempio nelle funzioni di START e STOP nei cronometri digitali; infatti la chiusura dei contatti elettrici può non avvenire in modo definitivo, ma dopo una serie di rimbalzi, i quali generano altrettanti impulsi che, interpretati erroneamente dal circuito logico, porterebbero ad errori di funzionamento. L'uso di un flip flop, di solito SR, il quale commuta la sua uscita al primo impulso e ignora i successivi, risolve il problema. Le tabelle di verità possono essere ricavate dalle equazioni caratteristiche.

Esistono diversi tipi: S-R, J-K, T, D-latch, D-Edge-Triggered.

Flip Flop

[modifica | modifica sorgente]I flip-flop (o bistabili) sono circuiti elettronici sequenziali molto semplici, utilizzati nell'elettronica digitale come dispositivi di memoria elementare. Il nome Flip-Flop deriva dal rumore che facevano i primi circuiti di questo tipo, costruiti con relè che permettevano il cambiamento di stato.

Possono essere utilizzati anche come circuito anti-rimbalzo per i contatti di un pulsante, un interruttore o un relè, indispensabili per esempio nelle funzioni di START e STOP nei cronometri digitali; infatti la chiusura dei contatti elettrici può non avvenire in modo definitivo, ma dopo una serie di rimbalzi, i quali generano altrettanti impulsi che, interpretati erroneamente dal circuito logico, porterebbero ad errori di funzionamento. L'uso di un flip flop, di solito SR, il quale commuta la sua uscita al primo impulso e ignora i successivi, risolve il problema. Le tabelle di verità possono essere ricavate dalle equazioni caratteristiche.

Esistono diversi tipi: S-R, J-K, T, D-latch, D-Edge-Triggered.

- Flip-flop SR o Latch SR

È il flip-flop più semplice dal punto di vista circuitale e fu anche il primo ad essere realizzato. La versione attiva alta ha due ingressi s (Set) e r (Reset, detto anche Clear) e due uscite q e q_ (q complementato). È una rete sequenziale asincrona (senza clock) che si evolve in accordo alle seguenti specifiche: quando lo stato d'ingresso è s=0 e r=1 il flip-flop si resetta, cioè porta a 0 il valore della variabile d'uscita q e a 1 la variabile d'uscita q_; quando lo stato d'ingresso è s=1 e r=0 il flip-flop si setta cioè porta a 1 il valore della variabile d'uscita q e a 0 la variabile d'uscita q_; quando lo stato d'ingresso è s=0 e r=0 il flip-flop conserva, cioè mantiene inalterato il valore di entrambe le variabili d'uscita. La combinazione s=1 ed r=1 non viene utilizzata in quanto instabile (il risultato dipende infatti da quale delle porte che compongono il circuito interno del flip flop viene commutata prima).

Quando entrambi i valori R e S sono bassi, il flip-flop si trova nello stato neutro e mantiene il valore delle uscite, in questo caso si dice che "fa memoria" (mantiene cioè in uscita il dato precedente memorizzato). Quando invece entrambi gli ingressi hanno valore 1, si ha una condizione logicamente non definita. Elettronicamente, con gli ingressi S e R contemporaneamente a 1, il circuito del flip-flop SR si trasforma in un oscillatore astabile la cui frequenza dipende dal ritardo di trasmissione delle porte logiche componenti; le uscite del flip-flop SR emettono allora due onde quadre di pari frequenza e sfasate di 180°. Questa "perdita di senso logico" che è possibile nei flip-flop SR è il motivo principale per cui, di norma, si impiegano flip-flop JK o D nei circuiti digitali.

Tabella di verità (Q+ e Qn+ (uscita negata) indicano gli stati futuri della memoria all'istante t+1 in base agli ingressi all'istante t):

| S | R | Q+ | Qn+ | Descrizione |

|---|---|---|---|---|

| 0 | 0 | Nc | Nc | Nessuna Commutazione |

| 1 | 0 | 1 | 0 | Set |

| 0 | 1 | 0 | 1 | Reset |

| 1 | 1 | - | - | Combinazione non utilizzata |

- Flip-flop JK

È caratterizzato da due ingressi, due uscite complementari e un ingresso di sincronizzazione. Ha funzioni di memoria, reset, set. A differenza dei Flip-flop SR non ha stati proibiti, ovvero le due entrate possono assumere qualsiasi valore (0-0,0-1,1-0,1-1).

Equazione caratteristica: Q+ = KnQ + JQn

Tabella di verità

| J | K | Q+ | Qn+ |

Descrizione |

|---|---|---|---|---|

| 0 | 0 | Q | Qn | Nessun Cambiamento |

| 1 | 0 | 1 | 0 | Set |

| 0 | 1 | 0 | 1 | Reset |

| 1 | 1 | Qn | Q | Toggle |

Quindi, quando J e K valgono entrambi 1, le uscite vengono complementate (ossia se erano 1 diventano 0 e viceversa), trasformandosi in un flip-flop T; quando valgono zero, vengono mantenute in memoria.

- Flip-flop T (toggle)

Ha un ingresso, due uscite complementari e un ingresso di sincronizzazione. Ha funzioni di memoria e toggle, che consiste nella negazione del valore precedentemente memorizzato. Può venir realizzato con un flip-flop JK, con i due ingressi J e K collegati assieme e formanti quindi l'ingresso T.

Equazione caratteristica: Q+ = TnQ + TQn = T ⊕ Q

Proprietà: Se T=1 l'uscita Q ha frequenza dimezzata rispetto al clock.

Applicazioni: È il componente base dei contatori, infatti collegando a cascata vari flip-flop T ad ogni uscita si ottiene un clock dimezzato rispetto al clock precedente.

Tabella di verità:

| T | Q+ | Descrizione |

|---|---|---|

| 0 | Q | memoria (nessun cambiamento) |

| 1 | Qn | complemento |

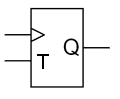

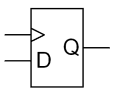

- Flip-flop D (delay)

Ha un ingresso per il dato, un ingresso di sincronizzazione (clock) e un'uscita. In corrispondenza del comando di clock, trasferisce l'ingresso in uscita e ve lo mantiene fin quando non cambia il suddetto ingresso. Se E=1, il latch è in trasparenza, cioè l'uscita Q insegue l'ingresso, vale a dire Q=D. Se E=0, il latch è in conservazione, ossia Q mantiene l'ultimo valore campionato. È POSSIBILE

Equazione caratteristica: Q+ =D

Applicazioni: per le sue caratteristiche è il componente base delle memorie (veloci) e registri (normali, a scorrimento, ad anello).

Tabella di verità:

| D | Q+ | Descrizione |

|---|---|---|

| 0 | 0 | reset |

| 1 | 1 | set |

- Circuiti integrati flip-flop

Sono disponibili circuiti integrati che contengono flip-flop singoli oppure multipli. Ad esempio il flip-flop di tipo D è disponibile come integrato con otto unità logiche ma con l’ingresso di clock in comune.[1]

Generalmente non sono disponibili in commercio flip-flop di tipo T, poiché sono facilmente realizzabili utilizzando un flip-flop JK con i due ingressi collegati tra di loro.

Componenti combinatori standard

[modifica | modifica sorgente]Encoder

[modifica | modifica sorgente]L'Encoder ha la funzione di rilevare l'attivazione di una determinata linea d'ingresso e riportare sulle uscite il codice binario dell'entrata corrispondente. Il funzionamento del dispositivo è tale che attivando una delle n linee in ingresso, l'uscita assume una delle m configurazioni possibili, solo a titolo di esempio per riportarci al decoder, ossia 8 ingressi avranno 3 uscite che in codice binario identificano i numeri da 0 a 7 tra ingresso e uscita non esiste però legame logico come nel decoder perché all'interno del encoder esistono delle allocazioni perenni di memoria (memorizzate dal costruttore) tali che il loro numero sia pari alle linee in ingresso (ogni linea attiva individua una locazione di memoria). Se gli ingressi attivati sono più di uno, l'uscita potrebbe assumere una configurazione binaria indesiderata. Per evitare che questo accada, i codificatori in commercio sono "con priorità": se si attiva più di una linea in ingresso, l'uscita assumerà la configurazione associata all'ingresso con più priorità, tra quelli attivati.

La tabella della verità permette di capire meglio cosa si intende per priorità. La configurazione n°0 presenta l'ingresso attivato, e i tre bit in uscita codificano la configurazione zero binario. La seconda riga presenta l'ingresso attivato, e le uscite codificano la configurazione n°1 in binario qualsiasi sia lo stato logico degli ingressi precedenti. L'ingresso ha quindi maggior priorità rispetto all'ingresso . Di conseguenza, l'ingresso ha maggiore priorità di e e così via sino all'ultima linea in ingresso.

decoder

[modifica | modifica sorgente]Il decoder o decodificatore, è una tipologia di componente utilizzato nell'elettronica digitale. La sua funzione è opposta a quella dell'encoder: in base alla combinazione dei bit presenti ai suoi ingressi, attiva una corrispondente combinazione di bit sulle linee di uscita.

In generale avendo n linee di ingresso, viene attivata esclusivamente una delle m linee di uscita con:

In base a questo il decodificatore viene detto n a m.

Esistono vari tipi di decodificatore: BCD-decimale (4 a 10), binario-ottale (2 a 8), binario-esadecimale (4 a 16), codice Gray-decimale, ecc.

Per esempio un decodificatore binario-decimale può essere rappresentato con la seguente tabella di verità:

D C B A | 0 1 2 3 4 5 6 7 8 9 --------+-------------------- 0 0 0 0 | 1 0 0 0 0 0 0 0 0 0 0 0 0 1 | 0 1 0 0 0 0 0 0 0 0 0 0 1 0 | 0 0 1 0 0 0 0 0 0 0 0 0 1 1 | 0 0 0 1 0 0 0 0 0 0 0 1 0 0 | 0 0 0 0 1 0 0 0 0 0 0 1 0 1 | 0 0 0 0 0 1 0 0 0 0 0 1 1 0 | 0 0 0 0 0 0 1 0 0 0 0 1 1 1 | 0 0 0 0 0 0 0 1 0 0 1 0 0 0 | 0 0 0 0 0 0 0 0 1 0 1 0 0 1 | 0 0 0 0 0 0 0 0 0 1 1 0 1 0 | 0 0 0 0 0 0 0 0 0 0 1 0 1 1 | 0 0 0 0 0 0 0 0 0 0 1 1 0 0 | 0 0 0 0 0 0 0 0 0 0 1 1 0 1 | 0 0 0 0 0 0 0 0 0 0 1 1 1 0 | 0 0 0 0 0 0 0 0 0 0 1 1 1 1 | 0 0 0 0 0 0 0 0 0 0 |

Questo decodificatore si trova nella condizione per cui . In questo caso, solo le prime 10, delle 16 combinazioni possibili sui 4 fili di ingresso, danno luogo ad una corrispondente combinazione sui 10 fili di uscita, le 6 combinazioni successive non danno luogo ad un'uscita, sono ininfluenti.

multiplexer

[modifica | modifica sorgente]

In elettronica, il termine può riferirsi ad una tipologia di circuiti integrati, oppure ad una particolare apparecchiatura completa. Nel primo caso un multiplexer o mux o selettore è un dispositivo capace di selezionare un singolo segnale elettrico fra diversi segnali in ingresso in base al valore degli ingressi di selezione. Esistono multiplexer sia per segnali digitali che per segnali analogici (amux).

Per esempio, un multiplexer a 2 ingressi è una semplice porta logica la cui uscita Y assume il valore di uno dei due ingressi A o B in base al valore del terzo ingresso di selezione S. L'equazione booleana è:

- Y = (A and not S) or (B and S)

Che può essere espressa dalla seguente tabella di verità:

| Input | Output | ||

|---|---|---|---|

| 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 |

Questa tabella di verità mostra che quando il selettore è uguale a "0", allora Y è collegato ad A; mentre quando il selettore è uguale ad "1", Y è dipendente da B.

Sono di uso comune multiplexer con molte porte. Per esempio, un multiplexer a otto ingressi può smistare otto diversi segnali, tramite tre segnali logici di selezione. I segnali di ingresso sono numerati da X0 a X7, e gli ingressi di selezione sono numerati S2, S1 e S0. Se S2 e S0 sono a '1' e S1 è a '0', per esempio, l'uscita sarà uguale a X5. In genere i multiplexer possono essere implementati con le porte logiche elementari, quali AND, OR, NAND ecc.

Di solito gli ingressi di selezione sono n, mentre le variabili in entrata sono o meno.

demultiplexer

[modifica | modifica sorgente]

Il dispositivo complementare, il demultiplexer, ha un solo ingresso e diverse uscite. Un demultiplexer è un circuito logico la cui principale funzione è inversa a quella del Multiplexer. Esso è quindi una rete combinatoria con k ingressi (di selezione) e uscite, ciascuna delle quali è attiva soltanto in corrispondenza di uno dei valori di ingresso. I piedini in basso (che si vedono anche in figura) sono detti di indirizzamento ( o ingresso di selezione). In base al valore degli ingressi di selezione, l'ingresso viene collegato a una delle uscite. Per esempio, un demux a otto uscite ha un segnale di ingresso (X), tre ingressi di selezione (S2, S1 e S0), e otto uscite (da A0 a A7). Se per esempio S2 e S0 sono a '1' e S1 è a '0', l'uscita A5 sarà uguale ad X e tutte le altre uscite saranno messe a 0. Il demultiplexer ha la funzione esattamente inversa al multiplexer: il multiplexer infatti riunisce più entrate in un'unica uscita mentre il demultiplexer smista un ingresso in più uscite.

parity checher

[modifica | modifica sorgente]In elettronica, e in particolare nell'architettura hardware dei calcolatori, il parity checker "verificatore di parità") e il parity generator ("generatore di parità") sono due circuiti combinatori deputati al controllo della corretta memorizzazione dei dati in memoria RAM attraverso la tecnica del bit di parità.

Ogni volta che un valore viene scritto in una cella della memoria RAM, il parity generator aggiunge ai dati scritti un bit "extra", impostato in modo tale che i bit posti a "1", in ogni cella, siano sempre pari (o sempre dispari a seconda delle implementazioni). In fase di lettura, il parity checker verifica che questo vincolo sia rispettato; se questo non risulta essere vero, ciò implica che almeno uno dei bit è stato memorizzato in modo scorretto, ovvero che è avvenuto un malfunzionamento della RAM. Questo errore viene segnalato al sistema operativo.

majority gate

[modifica | modifica sorgente]Una porta di maggioranza è una porta logica utilizzata nei circuiti complessi ed altre applicazioni di circuiti booleani. Una porta di maggioranza restituisce "vero" se e solo se più del 50% dei suoi ingressi sono "veri".

Per esempio, in un sommatore, l'uscita di riporto viene trovato applicando una funzione di maggioranza a tre ingressi, anche se spesso questa parte del sommatore si articoli in diverse porte logiche semplici.

full adder

[modifica | modifica sorgente]

| An | Bn | Cn-1 | Sn | Cn |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Il full-adder o sommatore completo è un componente elettronico digitale caratterizzato da tre ingressi e due uscite. La sua funzionalità è quella di eseguire una somma tra due numeri espressi in formato binario con lunghezza di parola a un bit. È un componente fondamentale dell'elettronica digitale perché, connesso opportunamente con altri full-adder e porte logiche può dare luogo alle unità di elaborazione ALU (Arithmetic Logic Unit) dei processori.Il Full-Adder sono le fondamenta su cui è basata la costruzione di semplici calcolatrici. Il full adder è costituito dall'insieme di due half-adder e una porta logica OR, opportunamente collegati (Figura a destra).

In logica binaria esegue questa semplice operazione:

A + B + Ri = S + Ro

dove A e B sono gli operandi, Ri il riporto in ingresso della precedente somma e S e Ro sono la somma e il riporto di uscita. Ogni variabile è un bit (0 oppure 1)

In ingresso sono inseriti i due bit da sommare e l'eventuale bit di riporto; in uscita vengono forniti la somma ed il riporto. Ad esempio, se diamo in ingresso i valori 1 1 0 (1° numero, 2° numero, riporto), il componente restituirà il valore 0 con riporto 1 (corrispondente al valore 10 in base binaria).

Full-adder a "n" bit

[modifica | modifica sorgente]La struttura col riporto in ingresso esiste per poter eventualmente collegare un numero "n" full-adder in cascata per poter ottenere Full-adder a "n" bit.

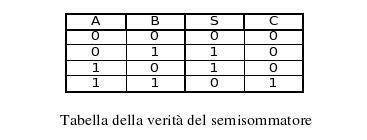

half adder

[modifica | modifica sorgente] Il circuito è costituito, di conseguenza, da una porta AND e una porta XOR.

Il circuito è costituito, di conseguenza, da una porta AND e una porta XOR.

comparatore

[modifica | modifica sorgente]Se le due parole sono costituite da un solo w:bit!bit, il circuito in grado di realizzare questa funzione è una semplice porta EX-OR a due ingressi, la quale presenta in uscita uno stato logico 0 quando i bit di ingresso sono uguali, quindi è un comparatore di uguaglianza ad uscita attiva bassa, utilizzando una porta EX-NOR si ottiene un comparatore di uguaglianza con uscita attiva alta. Per realizzare un comparatore per parole a più bit occorre confrontare i bit di uguale peso delle due parole, l'uscita segnalerà l'uguaglianza solo nel caso in cui tutti i bit corrispondenti risultano uguali.

Per esempio un comparatore che confronta due parole A e B di due bit ( e ) risulterà in questo modo: Sull'uscita E ci sarà un segnale alto solo se entrambi gli ingressi della porta AND sono a 1 cioè soltanto quando tutti i bit dello stesso peso sono uguali.

Lo stesso processo logico può essere esteso a parole con un numero qualsiasi di bit. A volte nei comparatori integrati, oltre all'uscita che segnala quando A=B, esistono anche altri terminali che danno un'indicazione di maggioranza e di minoranza, ossia se A>B oppure A<B, inoltre spesso sono presenti degli ingressi supplementari per il collegamento in cascata di più comparatori, in modo da poter analizzare parole formate da un maggior numero di bit. *Funzione analogica

Aritmetic Logic Unit

[modifica | modifica sorgente]

componenti architetturali

[modifica | modifica sorgente]architettura di Neumann

[modifica | modifica sorgente]

, Random Access Memory)

- Unità di input, tramite la quale i dati vengono inseriti nel calcolatore per essere elaborati

- Unità di output, necessaria affinché i dati elaborati possano essere restituiti all'operatore

- Bus, un canale che collega tutti i componenti fra loro

All'interno dell'ALU è presente un registro detto accumulatore, che fa da ponte tra input e output grazie a una speciale istruzione che carica una parola dalla memoria all'accumulatore e viceversa.

È importante sottolineare che tale architettura, a differenza di altre, si distingue per la caratteristica di immagazzinare all'interno dell'unità di memoria, sia i dati dei programmi in esecuzione che il codice di questi ultimi.

Bisogna comunque precisare che questa è una schematizzazione molto sintetica, sebbene molto potente: basti pensare che i moderni computer di uso comune sono progettati secondo l'architettura Von Neumann. Difatti essa regola non solo gli insiemi, ma l'intera architettura logica interna degli stessi, ovvero la disposizione delle porte logiche, perlomeno per quanto riguarda la parte elementare, sulla quale si sono sviluppate le successive progressioni.

Inoltre, quando si parla di unità di memoria si intende la memoria primaria, mentre le memorie di massa sono considerate dispositivi di I/O.

Il motivo di ciò è innanzitutto storico, in quanto negli anni 1940, epoca a cui risale questa architettura, la tecnologia non lasciava neanche presupporre dispositivi come hard disk, CD-ROM, DVD-ROM o anche solo nastri magnetici, ma anche tecnico, se si considera che in effetti i dati da elaborare devono comunque essere caricati in RAM, siano essi provenienti da tastiera o da hard-disk.

Architettura di Harvard

[modifica | modifica sorgente]

In informatica, l'architettura Harvard è un tipo di architettura hardware per computer digitali in cui vi è separazione tra la memoria contenente i dati e quella contenente le istruzioni. Il termine inizialmente indicava l'architettura del computer Harvard Mark I, un computer basato su relè che memorizzava le istruzioni su un nastro perforato mentre i dati venivano memorizzati in un contatore elettromeccanico a 23 cifre. Questa macchina non era dotata di un'unità di immagazzinamento dei dati, questi erano interamente memorizzati dalla CPU e il loro caricamento e salvataggio era un processo eseguito in modo manuale agendo sui contatori.

Voci correlate

[modifica | modifica sorgente]divisore di frequenza

[modifica | modifica sorgente]Il divisore di frequenza è un circuito elettronico che prende in ingresso un segnale con una certa frequenza e genera in uscita un segnale con frequenza:

dove è un intero. I sintetizzatori di frequenza ottenuti con le phase-locked loop usano i divisori di frequenza per ottenere un'uscita a una frequenza multipla di quella di un certo segnale di riferimento. Esistono per i divisori di frequenza sia implementazioni di tipo analogico che digitale.

Registri

[modifica | modifica sorgente]I registri costituiscono il punto più alto della gerarchia della memoria, e sono il meccanismo più rapido per il sistema di manipolare i dati. I registri sono normalmente misurati in base al numero di bit che possono contenere (ad esempio, registri a 8 bit o registri a 32 bit]). Attualmente i registri sono implementati normalmente con file di registro, ma in passato sono stati implementati usando flip flop individuali, memoria a nuclei di ferrite ad alta velocità, memoria thin film e vari altri modi.

Il termine è usato spesso per riferirsi esclusivamente al gruppo di registri che possono essere direttamente indirizzati dalle istruzioni di input e output del microprocessore. Più propriamente, queste registri sono definiti "architected registers". Per esempio, nell'architettura x86 è disponibile un set di otto registri utilizzabili dalle istruzioni del linguaggio macchina, ma la CPU conterrà molti più registri per uso interno o con funzioni speciali.

Memorie

[modifica | modifica sorgente]In ambito informatico la memoria è la parte del computer destinata a conservare i dati nel tempo, la cui implementazione fisica dà vita ai vari supporti di memorizzazione esistenti. La memorizzazione di informazioni in memoria, e il successivo recupero delle medesime, sono funzioni fondamentali nei processi di elaborazione dati.

È una parte essenziale nonché una delle chiavi di successo (assieme alla capacità di processamento e alla riprogrammabilità) del computer grazie alla possibilità di memorizzare, nei moderni sistemi elettronici, grandi quantità di dati. In essa sono memorizzati dati d'archivio dell'utente e le istruzioni dei programmi facenti parte del software di base o applicativo.

Una memoria può essere considerata astrattamente come una sequenza finita di celle in cui ogni cella contiene una sequenza finita di bit, normalmente gestiti a gruppi di otto detti byte. Pertanto lo spazio fisico della memoria può essere immaginato come una sequenza di posizioni, ognuna contenente un byte. Ogni posizione è individuata da un preciso indirizzo di memoria, normalmente espresso tramite un numero intero positivo.

- ↑ (EN) Circuito integrato 74HC374 costituito da otto flip-flop di tipo D con ingresso di clock in comune ed in più un controllo (prioritario) di abilitazione/disabilitazione delle uscite (PDF), su onsemi.com, ON Semiconductor Corp. URL consultato il 4 giugno 2010.