Sistemi e tecnologie elettroniche/Circuiti logici: caratteristiche elettriche e interfacciamento

Invertitore CMOS con carico resistivo

[modifica | modifica sorgente]-

Circuito equivalente di un invertitore CMOS allo stato alto H collegato a un carico resistivo verso massa

-

Circuito equivalente di un invertitore CMOS allo stato basso L collegato a un carico resistivo verso l'alimentazione

Uscita a stato H, carico verso massa

[modifica | modifica sorgente]

Il circuito impone una retta di carico sulla resistenza di carico:[1]

La resistenza di carico non deve essere troppo piccola affinché il punto di funzionamento del circuito non esca dal valore limite :

Uscita a stato L, carico verso alimentazione

[modifica | modifica sorgente]

Il circuito impone una retta di carico sulla resistenza di perdita dell'inverter:

La resistenza di carico non deve essere troppo piccola affinché il punto di funzionamento del circuito non esca dal valore limite :

Invertitori con carico capacitivo

[modifica | modifica sorgente]La presenza di una capacità nel carico introduce degli effetti capacitivi di ritardo: le commutazioni non sono istantanee.

Nella realtà sono presenti anche degli effetti induttivi che introducono delle piccole oscillazioni nel segnale.

Ritardi di transizione

[modifica | modifica sorgente]Si definisce tempo di transizione l'intervallo di tempo impiegato dal segnale per variare la sua ampiezza tra il 10% e il 90%. Si distinguono il tempo di salita e il tempo di discesa :

Il tempo di transizione , sia nel fronte di salita sia nel fronte di discesa, è direttamente proporzionale alla costante di tempo :

Transizione L → H

[modifica | modifica sorgente]

Il condensatore passa da circuito aperto a cortocircuito → la tensione di uscita ha un andamento esponenziale crescente che parte dalla tensione e tende alla tensione con costante di decadimento :[2]

Transizione H → L

[modifica | modifica sorgente]

Il condensatore passa da cortocircuito a circuito aperto → la tensione di uscita ha un andamento esponenziale decrescente che parte dalla tensione e tende alla tensione con costante di decadimento :[2]

Invertitore nMOS

[modifica | modifica sorgente]

La resistenza equivalente di uscita vale nello stato H e nello stato L → è molto più piccola quando l'interruttore è chiuso → la costante di tempo del fronte di salita risulta molto più piccola → il tempo di transizione L → H è maggiore del tempo di transizione H → L.

Invertitore CMOS

[modifica | modifica sorgente]

L'elemento di pull-up non è più passivo ma attivo: cambia il suo valore di resistenza equivalente in funzione dell'ingresso esattamente come fa l'elemento di pull-down → il comportamento dinamico è simmetrico e i tempi di transizione sono entrambi piccoli.

Si possono minimizzare i ritardi riducendo la costante di tempo, in particolare:

- la resistenza equivalente vista ai morsetti del condensatore → la corrente che scorre all'uscita diventa elevata;

- la capacità equivalente → il dispositivo deve essere piccolo (ad esempio, nel transistore MOS la capacità , cioè la capacità equivalente per unità di superficie,[3] si estende all'intero volume moltiplicandola per l'area ) → conferma la legge di Moore.

Ritardi di propagazione

[modifica | modifica sorgente]Una variazione all'ingresso viene propagata all'uscita con un certo ritardo: si definisce tempo di propagazione della porta l'intervallo di tempo tra l'istante in cui il segnale d'ingresso ha il 50% di ampiezza e l'istante in cui il segnale d'uscita ha il 50% di ampiezza:

La costante di tempo, e quindi il tempo di transizione, dipende anche dalla parte capacitiva del carico: collegare l'invertitore a un circuito digitale con un numero di ingressi, detto fan out, troppo grande aumenta la capacità equivalente di carico, rischiando che il tempo di transizione superi il tempo di propagazione e il segnale non abbia il tempo di commutare.[non chiaro]

Collegamento a bus

[modifica | modifica sorgente]In un collegamento a bus non è noto a priori il numero di dispositivi logici connessi → bisogna evitare le collisioni, cioè due dispositivi non devono comunicare sul bus in contemporanea.

Uscita totem pole (TP)

[modifica | modifica sorgente]

Collegare tra loro le uscite di più invertitori CMOS può essere pericoloso: siccome i vari segnali di controllo sono indipendenti tra loro, un'errata combinazione di essi può far andare l'alimentazione in cortocircuito.

Uscita a tre stati (3S)

[modifica | modifica sorgente]

In un collegamento a bus con uscite a tre stati, ogni circuito ha un segnale di enable, e i segnali di enable vengono attivati uno alla volta da un modulo di controllo per evitare le collisioni:

- segnale di enable allo stato basso L: l'uscita del circuito è abilitata (come totem pole);

- segnale di enable allo stato basso H: l'uscita del circuito viene disabilitata e assume un terzo stato Hi-Z (ad alta impedenza).

Il segnale di enable può essere rappresentato circuitalmente con un unico deviatore a 3 posizioni, di cui una corrisponde allo stato Hi-Z, oppure con un altro deviatore in serie all'uscita che abilita o disabilita l'uscita a seconda se chiuso o aperto:

La non idealità del circuito aperto interpretato nello stato Hi-Z è rappresentabile con una corrente di perdita .

L'uscita a tre stati è pericolosa se non si può garantire di poter attivare i segnali di enable solo uno alla volta.

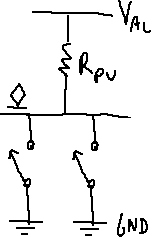

Uscita a collettore aperto (OC)

[modifica | modifica sorgente]

L'uscita a collettore aperto (open drain) trova applicazione nella gestione delle richieste di interrupt, dove possono verificarsi più richieste alla volta.

Ogni stadio di uscita è realizzato con un solo interruttore nMOS verso massa.

Tutti gli stadi di uscita sono in parallelo e condividono un'unica resistenza di pull-up :

- wired or: la linea va nello stato basso L se anche una sola uscita è chiusa;

- wired and: la linea va nello stato alto H solo se tutte le uscite sono aperte.

Nel caso dell'inverter, l'interruttore è chiuso se l'ingresso è allo stato alto H e viceversa:

- operatore NOR (uscita 0 quando almeno uno degli ingressi è 1): basta che uno solo degli interruttori sia chiuso perché la linea scenda allo stato basso L;

- operatore NAND (uscita 0 quando tutti gli ingressi sono 1): tutti gli interruttori devono essere aperti perché la linea salga allo stato alto H.

Collegando carichi a uscite OC, è necessario scegliere una resistenza di pull-up che garantisca la compabilità statica, cioè la corrente e la tensione non devono superare i valori limite riconosciuti dai carichi:

La scelta del valore di resistenza è quindi un compromesso tra due caratteristiche del dispositivo:

- : massimizza la velocità perché è minore la resistenza equivalente e quindi la costante di tempo ;

- : minimizza la potenza dissipata perché la corrente che scorre attraverso la resistenza è minore.

Segnali differenziali digitali

[modifica | modifica sorgente]Anche i segnali digitali possono essere trasmessi in modo differenziale: lungo due fili, entrambi riferiti al terzo filo di massa, scorrono due segnali digitali uno invertito all'altro, e il segnale logico di informazione è dato dalla loro differenza.

- Vantaggi

- immunità ai disturbi dall'esterno;

- minor consumo: i gradini dei singoli segnali hanno metà ampiezza del segnale differenziale allo stato alto H → è richiesta una tensione di alimentazione minore di quella richiesta da un singolo segnale di modo comune di ampiezza doppia.

Note

[modifica | modifica sorgente]- ↑ È chiamata resistenza la resistenza di perdita del transistore pMOS quando l'uscita dell'inverter è allo stato alto H, e viceversa per la resistenza . L'altro effetto di non idealità, la corrente di perdita , verrà sempre trascurato.

- ↑ 2,0 2,1 La resistenza di carico non deve essere troppo piccola perché, quando ad esempio il condensatore è un circuito aperto, la tensione di alimentazione si ripartirebbe in una tensione di uscita troppo piccola → la qualità del segnale viene degradata.

- ↑ Nel sistema MOS, la superficie è perpendicolare alla lunghezza del canale .