Elettronica applicata/Circuiti logici

In elettronica gli stati logici 0 e 1 sono associati ai due valori di tensione alta e bassa :

- convenzione logica positiva: 1 ⟷ | 0 ⟷

- convenzione logica negativa: 0 ⟷ | 1 ⟷

Si definisce una tensione di soglia al di sotto della quale il segnale analogico viene riconosciuto nello stato logico L, e viceversa.

Per un segnale analogico proveniente dall'uscita di un circuito digitale, sono definiti due valori limite di tensione:

- è il valore di tensione minimo per l'uscita U allo stato H;

- è il valore di tensione massimo per l'uscita U allo stato L.

Affinché questo segnale venga riconosciuto correttamente all'ingresso di un circuito digitale, sono definiti altri due valori limite:

- è il valore di tensione minimo per l'ingresso I allo stato H;

- è il valore di tensione massimo per l'ingresso I allo stato L.

Per compatibilità si intende la capacità di circuiti connessi in cascata di scambiarsi correttamente stati logici: gli ingressi devono interpretare correttamente i livelli di tensione.

Due circuiti logici appartenenti alla stessa famiglia logica hanno le stesse caratteristiche elettriche (alimentazione, tensioni e correnti di uscita e di ingresso, ritardi, consumo) → sono elettricamente compatibili tra di loro.

Conviene evitare valori limite ingresso-uscita uguali garantendo un margine di rumore per ridurre l'effetto dei disturbi:

Per recuperare un segnale digitale disturbato, si può interporre fra due circuiti digitali un comparatore di soglia, un modulo che realizza una funzione a gradino: converte un ingresso analogico, in base a un unico valore di soglia , in un valore logico/binario in uscita.

La transcaratteristica di un invertitore reale non è brusca ma segue una variazione continua e graduale attraverso uno stato logico non definito.

Sulla transcaratteristica, i valori limite di tensione sono definiti di solito come i punti in cui le tangenti al grafico hanno pendenza 45°. È impossibile definire con precisione la tensione di soglia perché varia con l'alimentazione, la temperatura, ecc.

Parametri elettrici statici

[modifica | modifica sorgente]Struttura dell'invertitore CMOS

[modifica | modifica sorgente]

Nell'invertitore CMOS (o a MOS complementari), l'uscita tramite due interruttori è collegata:

- alla tensione di alimentazione per avere lo stato alto H in uscita;

- o

- a massa per avere lo stato basso L in uscita.

Vi sono delle resistenze di perdita : verso l'alimentazione, verso massa. L'invertitore CMOS è realizzato tramite un transistore pMOS verso e un transistore nMOS verso massa.[1]

Parametri di uscita

[modifica | modifica sorgente]-

Circuito equivalente di un invertitore CMOS allo stato alto H collegato a un carico resistivo verso massa

-

Circuito equivalente di un invertitore CMOS allo stato basso L collegato a un carico resistivo verso l'alimentazione

In presenza di carichi (diodi LED, resistenze...), la corrente in uscita deve essere limitata, altrimenti la tensione d'uscita supererebbe i campi di valori garantiti:[2]

- allo stato alto H, all'intersezione tra la caratteristica della porta e la caratteristica del carico :

- deve essere garantita la condizione → occorre limitare la corrente di uscita: ;[3]

- allo stato basso L, all'intersezione tra la caratteristica della porta e la caratteristica del carico :

- deve essere garantita la condizione → occorre limitare la corrente di uscita: .

Parametri di ingresso

[modifica | modifica sorgente]Analogamente anche la corrente in ingresso deve essere limitata per garantire la condizione sulla tensione di ingresso :

- è la corrente oltre la quale la tensione d'ingresso non è più minore di ;

- è la corrente oltre la quale la tensione d'ingresso non è più maggiore di .

Configurazioni di uscita

[modifica | modifica sorgente]In un collegamento a bus non è noto a priori il numero di dispositivi logici connessi → bisogna evitare le collisioni, cioè due dispositivi non devono comunicare sul bus in contemporanea.

Uscita totem pole (TP)

[modifica | modifica sorgente]

L'uscita totem pole può essere vista come un deviatore tra e massa:

- allo stato alto H la tensione di uscita è prossima alla tensione di alimentazione ;

- allo stato basso L la tensione di uscita è prossima a 0 ().

Uscita a tre stati (3S)

[modifica | modifica sorgente]

In un collegamento a bus con uscite a tre stati, ogni circuito ha un segnale di enable, e i segnali di enable vengono attivati uno alla volta da un modulo di controllo per evitare le collisioni:

- segnale di enable allo stato basso L: l'uscita del circuito è abilitata (come totem pole);

- segnale di enable allo stato alto H: l'uscita del circuito viene disabilitata e assume un terzo stato Hi-Z (ad alta impedenza).

Il segnale di enable può essere rappresentato circuitalmente con un unico deviatore a 3 posizioni, di cui una corrisponde allo stato Hi-Z, oppure con un altro deviatore in serie all'uscita che abilita o disabilita l'uscita a seconda se chiuso o aperto:

La non idealità del circuito aperto interpretato nello stato Hi-Z è rappresentabile con una corrente di perdita .

L'uscita a tre stati è pericolosa se non si può garantire di poter attivare i segnali di enable solo uno alla volta.

Uscita a collettore aperto (OC)

[modifica | modifica sorgente]

L'uscita a collettore aperto (open drain) trova applicazione nella gestione delle richieste di interrupt, dove possono verificarsi più di una richiesta alla volta.

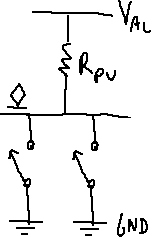

Ogni stadio di uscita è realizzato con un solo interruttore nMOS verso massa.

Tutti gli stati di uscita sono in parallelo e condividono un'unica resistenza di pull-up :

- wired or: la linea va nello stato basso L se anche un solo interruttore è chiuso;

- wired and: la linea va nello stato alto H solo se tutti gli interruttori sono aperti.

Ogni interruttore è quindi in grado di pilotare solo lo stato basso L. Se esso è aperto lo stato di uscita è solo disabilitato (Hi-Z); in questo caso si considera come elemento di non idealità una corrente di perdita .

Collegando carichi a uscite OC, è necessario scegliere una resistenza di pull-up che garantisca la compabilità statica, cioè la corrente e la tensione non devono superare i valori limite riconosciuti dai carichi:

La scelta del valore di resistenza è quindi un compromesso tra due caratteristiche del dispositivo:

- : massimizza la velocità perché è minore la resistenza equivalente e quindi la costante di tempo ;

- : minimizza la potenza dissipata perché la corrente che scorre attraverso la resistenza è minore.

Parametri dinamici

[modifica | modifica sorgente]La presenza di una capacità nel carico introduce degli effetti capacitivi di ritardo: le commutazioni non sono istantanee.

Tempi di transizione e di propagazione

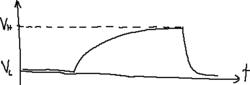

[modifica | modifica sorgente]Si definisce tempo di transizione l'intervallo di tempo impiegato dal segnale per variare la sua ampiezza tra il 10% e il 90%. Si distinguono il tempo di salita e il tempo di discesa :

Una variazione all'ingresso viene propagata all'uscita con un certo ritardo: si definisce tempo di propagazione della porta l'intervallo di tempo tra l'istante in cui il segnale d'ingresso ha il 50% di ampiezza e l'istante in cui il segnale d'uscita ha il 50% di ampiezza:

Ritardi di trasmissione

[modifica | modifica sorgente]Il carico capacitivo introduce un ritardo nel riconoscimento della variazione di stato da parte della porta d'ingresso:

- nella transizione L → H, il condensatore passa da circuito aperto a cortocircuito → la tensione di uscita ha un andamento esponenziale crescente che parte dalla tensione e tende alla tensione :

- nella transizione H → L, il condensatore passa da cortocircuito a circuito aperto → la tensione di uscita ha un andamento esponenziale decrescente che parte dalla tensione e tende alla tensione :

Il ritardo di trasmissione è il tempo impiegato dall'ingresso per riconoscere la variazione di stato. La variazione di stato viene riconosciuta quando viene superata la tensione di soglia .

La tensione di soglia non è univocamente definita → il ritardo di trasmissione è variabile.

Invertitori nMOS e CMOS

[modifica | modifica sorgente]Nell'invertitore nMOS la resistenza equivalente di uscita vale nello stato H e nello stato L → è molto più piccola quando l'interruttore è chiuso → la costante di tempo del fronte di salita risulta molto più piccola → il tempo di transizione L → H è maggiore del tempo di transizione H → L.

Nell'invertitore CMOS, invece, l'elemento di pull-up non è più passivo ma attivo: cambia il suo valore di resistenza equivalente in funzione dell'ingresso esattamente come fa l'elemento di pull-down → il comportamento dinamico è simmetrico e i tempi di transizione sono entrambi piccoli.

Minimizzazione dei ritardi

[modifica | modifica sorgente]

La costante di tempo, e quindi il tempo di transizione, dipende anche dalla parte capacitiva del carico: collegare l'invertitore a un circuito digitale con un numero di ingressi, detto fan out, troppo grande aumenta la capacità equivalente di carico, rischiando per commutazioni veloci (nell'ordine delle centinaia di MHz) che il tempo di transizione (ad es. 20 ns invece di 5 ns a causa di un elevato fan out) superi il tempo di commutazione (ad es. 10 ns) e il segnale non abbia il tempo di commutare tra uno stato logico e l'altro.

Un pass gate, cioè un MOS inserito in serie tra l'uscita e l'ingresso, aumenta ancora di più il ritardo perché aggiunge una parte resistiva e capacitiva aumentando la costante di tempo :

Per avere bassi ritardi occorre minimizzare la resistenza d'uscita e minimizzare la capacità equivalente degli ingressi.[4] Nell'invertitore CMOS si possono minimizzare i ritardi riducendo la costante di tempo, in particolare:

- la resistenza equivalente vista ai morsetti del condensatore → la corrente che scorre all'uscita diventa elevata;

- la capacità equivalente → il dispositivo deve essere piccolo (ad esempio, nel transistore MOS la capacità , cioè la capacità equivalente per unità di superficie,[5] si estende all'intero volume moltiplicandola per l'area ) → conferma la legge di Moore.

Segnali differenziali

[modifica | modifica sorgente]| Per approfondire, vedi Sistemi e tecnologie elettroniche - 5. Circuiti con amplificatori operazionali ideali. |

Anche i segnali digitali possono essere trasmessi in modo differenziale: lungo due fili, entrambi riferiti al terzo filo di massa, scorrono due segnali digitali uno invertito all'altro, e il segnale logico di informazione è dato dalla loro differenza.

- Vantaggi

- immunità ai disturbi dall'esterno;

- minor consumo: i gradini dei singoli segnali hanno metà ampiezza del segnale differenziale allo stato alto H → è richiesta una tensione di alimentazione minore di quella richiesta da un singolo segnale di modo comune di ampiezza doppia.

Note

[modifica | modifica sorgente]- ↑ In realtà si usano tipicamente più di due transistori per far avvicinare la transcaratteristica maggiormente all'idealità.

- ↑ Se l'uscita dell'invertitore CMOS viene collegata all'ingresso (gate) di un transistore MOSFET, la corrente di uscita è addirittura trascurabile.

- ↑ Per convenzione la corrente si considera sempre positiva entrante → in questo caso la corrente è negativa e la si considera in modulo.

- ↑ La resistenza di ingresso nei circuiti moderni è sempre approssimabile a un circuito aperto.

- ↑ Nel sistema MOS, la superficie è perpendicolare alla lunghezza del canale .