Elettronica applicata/Protocolli di bus

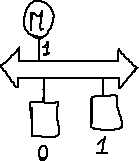

Una transazione è una sequenza di cicli di trasferimento, che sposta informazioni legate da un significato (indirizzo, dati, vettore di priorità...). In una transazione comunicano due unità:

- master: avvia l'operazione (es. CPU, DMA controller);

- slave: risponde ai comandi del master (es. memoria, periferiche di I/O).

In un sistema multi-punto tutte le unità condividono lo stesso canale, detto bus, costituito da un fascio di conduttori che connette tra loro tutte le coppie master-slave. Tutte le unità devono seguire lo stesso protocollo di transazione. Questo sistema è detto modulare aperto perché la configurazione del sistema può essere modificata aggiungendo o rimuovendo a piacere le schede.

Allocazione

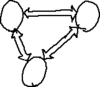

[modifica | modifica sorgente]Solo un master alla volta può prendere il controllo del bus → un meccanismo di allocazione del canale garantisce che il bus sia pilotato da un solo master alla volta ed evita così le collisioni.

Token passing

[modifica | modifica sorgente]Il segnale di concessione del bus, detto grant, viene passato da un master all'altro secondo un ordine prestabilito, e ogni master quando fa richiesta aspetta il suo turno.

Collision detection

[modifica | modifica sorgente]Tutti i master richiedenti possono parlare sul bus in qualunque momento, ma deve esistere un meccanismo di collision detection in grado di rilevare la collisione (es. CSMA/CD).

Arbitraggio

[modifica | modifica sorgente]

Un arbitro esamina le richieste e concede il grant secondo un criterio di arbitraggio:

- First Come First Served (FCFS)

L'arbitro segue l'ordine temporale delle richieste, ma è impossibile avere una risoluzione temporale infinita per le richieste quasi simultanee.

- Priorità

Ogni richiesta è associata a una certa priorità prestabilita, e vengono servite per prime le richieste a priorità maggiore → una sequenza ravvicinata di richieste ad alta priorità possono condannare alla starvation le richieste a bassa priorità, ovvero queste ultime non vengono mai servite perché hanno sempre la priorità richieste a priorità maggiore:

- Priorità con fairness

Il meccanismo di fairness impedisce la starvation delle richieste a bassa priorità: l'arbitro crea in un certo istante un'istantanea delle richieste attive, le serve secondo le loro priorità ignorando tutte le nuove richieste che giungono nel frattempo, e alla fine quando tutte le richieste nell'istantanea sono state servite crea una nuova istantanea e ripete la procedura.

Indirizzamento

[modifica | modifica sorgente]Lo slave con cui vuole comunicare il master viene selezionato tramite l'indirizzamento.

All'interno di una unità slave si possono riconoscere:

- decoder di indirizzi: riconosce l'indirizzo fornito dal master;

- unità di controllo e temporizzazione: gestisce l'handshake (strobe/ACK);

- core (es. celle di memoria nel caso di una memoria);

- data buffer (es. transceiver).

- Modalità di indirizzamento

- lineare: c'è un filo per ogni coppia master-slave, e lo slave viene selezionato direttamente attivando il suo filo → è possibile selezionare più slave alla volta, ma è adatto solo per sistemi con pochi slave;

- codificato: il master scrive l'indirizzo dello slave sul bus, e lo slave deve riconoscere tale indirizzo come il suo.

- logico: ogni slave è identificato da un indirizzo indipendentemente dalla sua posizione lungo il bus, quindi l'indirizzamento continua a funzionare anche se avviene lo scambio di due slave;

- geografico: l'indirizzo dello slave dipende dalla sua posizione lungo il bus, quindi il master non si accorge dello scambio di due slave.

Tecniche di miglioramento delle prestazioni

[modifica | modifica sorgente]Il throughput di un bus è il numero di bit trasferito nell'unità di tempo:

dove:

- è la larghezza del bus, cioè il numero di bit per ogni ciclo (numero di fili in parallelo);

- è la velocità del bus, cioè il numero di cicli nell'unità di tempo;

- è la durata di ogni ciclo di bus, e dipende da:

- parametri elettrici: , ;

- parametri dei moduli: , , ...;

- protocollo: numero di transizioni per ciclo, tipo di protocollo...

Migliorare le prestazioni significa aumentare il throughput :

- aumentare il numero di bit per ogni ciclo, ovvero ridurre il numero dei fili a parità di bit trasportati;

- ridurre la durata dei cicli.

Bus multiplexato

[modifica | modifica sorgente]In un normale bus parallelo i segnali di indirizzo e di dato usano fili separati in cicli successivi, quindi in tempi diversi → il bus multiplexato ottimizza l'uso dei fili: sia i segnali di indirizzo sia quelli di dato viaggiano sullo stesso fascio di fili, quindi a parità di numero di fili è possibile trasferire più bit.

Ottimizzazione del numero di transizioni

[modifica | modifica sorgente]

Le memorie DDR quasi dimezzano la durata dei cicli rimuovendo le transizioni inutili dei segnali di controllo strobe e ACK (dual-edge handshake) → si riduce il consumo di energia e aumenta il throughtput , anche se l'hardware è più complesso perché deve riconoscere una successione più complessa di transizioni di stato.

Protocollo Source Synchronous

[modifica | modifica sorgente]Prevede solo operazioni di scrittura: i segnali di informazione e di comando (strobe) viaggiano insieme, e arrivano alla destinazione con un ritardo l'uno dall'altro al massimo pari allo skew.

- Parametri di temporizzazione

- latenza dei dati: indica il tempo di attesa per ricevere i dati, e dipende da un solo tempo di trasmissione e dallo skew;

- frequenza di ciclo: è l'inverso della durata del ciclo, e non dipende dal tempo di trasmissione ma solo dallo skew.

- Confronto prestazioni

- protocollo sincrono: la velocità dipende dalla periferica più lenta;

- protocollo asincrono: la velocità è adattativa;

- protocollo semisincrono: è il più lento perché bisogna aspettare l'eventuale segnale di wait dal dispositivo più distante;

- protocollo Source Synchronous: è il più veloce perché non si deve attendere alcuna risposta → è usato per le RAM ad alta velocità.

Burst transfer

[modifica | modifica sorgente]

Spesso un'operazione di lettura, soprattutto da una memoria, viene effettuata su celle di indirizzo contiguo (località del software) → è possibile leggere una serie di locazioni di memoria sequenziale inviando solo il primo indirizzo, e un controllore situato nella memoria si occupa di incrementare l'indirizzo da cui leggere a ogni ciclo di dati.