Elettronica applicata/Circuiti sequenziali I

Tipi di flip-flop

[modifica | modifica sorgente]In un circuito combinatorio, i valori di uscita dipendono esclusivamente dai valori applicati ai suoi ingressi in quell'istante. In un circuito sequenziale, il valore di uscita dipende anche da ciò che è successo negli istanti precedenti. I circuiti sequenziali devono contenere elementi di memoria chiamati flip-flop.

Elemento base di memoria

[modifica | modifica sorgente]L'elemento base di memoria è composto da due inverter collegati in modo tale che l'uscita di uno è l'ingresso dell'altro (anello di inverter):

Dall'incrocio delle transcaratteristiche dei due inverter si possono individuare tre punti di funzionamento:

- , (stato stabile);

- questo punto di funzionamento è da evitare perché il livello logico non è definito univocamente (stato metastabile: è sufficiente un piccolo disturbo per uscire da questo stato e passare a uno stato stabile);

- , (stato stabile).

Flip-flop set reset asincroni

[modifica | modifica sorgente]Il flip-flop set-reset asincrono è un elemento di memoria in cui si può forzare o mantenere un certo valore binario a seconda della scelta dei due ingressi S e R.

Flip-flop set reset asincroni di NOR

[modifica | modifica sorgente]-

Struttura interna di un flip-flop set reset asincrono di NOR

-

Simbolo funzionale di un flip-flop set reset asincrono di NOR

| Ingressi | Uscite | Note | ||

|---|---|---|---|---|

| S | R | Q | Q* | |

| 1 | 0 | 1 | 0 | Viene forzato in uscita il valore 1. |

| 0 | 1 | 0 | 1 | Viene forzato in uscita il valore 0. |

| 0 | 0 | invariato | invariato | L'uscita mantiene il suo valore costante. |

| 1 | 1 | 0 | 0 | È una configurazione vietata perché le due uscite Q e Q* assumono lo stesso stato e non sono più complementari. |

In un sistema basato su un deviatore meccanico, alla commutazione il contatto rimbalza più volte dando origine a transizioni multiple in uscita. Per garantire che il segnale di uscita abbia una singola commutazione è possibile rendere il sistema anti-rimbalzo inserendo opportunamente un flip-flop:

Flip-flop set reset asincroni di NAND

[modifica | modifica sorgente]-

Struttura interna di un flip-flop set reset asincrono di NAND

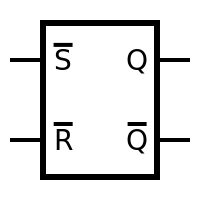

-

Simbolo funzionale di un flip-flop set reset asincrono di NAND

| Ingressi | Uscite | Note | ||

|---|---|---|---|---|

| S* | R* | Q | Q* | |

| 1 | 0 | 0 | 1 | Viene forzato in uscita il valore 0. |

| 0 | 1 | 1 | 0 | Viene forzato in uscita il valore 1. |

| 1 | 1 | invariato | invariato | L'uscita mantiene il suo valore costante. |

| 0 | 0 | 1 | 1 | È una configurazione vietata perché le due uscite Q e Q* assumono lo stesso stato e non sono più complementari. |

Flip-flop set reset sincroni

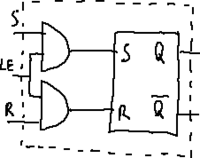

[modifica | modifica sorgente]Nel flip-flop set reset sincrono (latch) il segnale di abilitazione ad onda quadra LE si duplica in due segnali posti agli ingressi di due porte AND in coppia con entrambi gli ingressi S e R:

- transparent mode (LE = 1): il flip-flop è sensibile alle variazioni di livello degli ingressi S e R;

- latched mode (LE = 0): il flip-flop mantiene il suo valore senza vedere gli ingressi S e R, lasciando così il tempo al nuovo valore di propagarsi.

Due ulteriori segnali P (preset) e C (clear), che non devono mai essere entrambi a 1, servono per forzare in modo asincrono il flip-flop rispettivamente a 1 o a 0:

-

Struttura interna di un flip-flop latch dotato di comandi asincroni

-

Simbolo funzionale di un flip-flop latch dotato di comandi asincroni

Flip-flop D

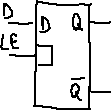

[modifica | modifica sorgente]Latch D

[modifica | modifica sorgente]Nel latch D, S e R sono uniti, attraverso una porta NOT, in un unico ingresso D che permette di forzare una coppia di valori S ≠ R. In questo modo i flip-flop di tipo D rendono impossibile il verificarsi della configurazione vietata.

Flip-flop master-slave D

[modifica | modifica sorgente]Un flip-flop master-slave D è costituito da due flip-flop latch in cascata con abilitazione complementare (cioè il clock del master è invertito rispetto al clock dello slave). L'ingresso viene campionato a istanti ben precisi, che sono i fronti di salita del segnale di clock:

- alla transizione 0 → 1, il valore corrente di Q' viene memorizzato dal master (in latched mode) e viene riportato in uscita Q dallo slave (in transparent mode);

- alla transizione 1 → 0, il master è in transparent mode e Q' diventa sensibile alle variazioni dell'ingresso D, ma indipendentemente da Q' lo slave (in latched mode) memorizza il valore corrente di Q e lo mantiene costante in uscita.

Il flip-flop D dual edge è in grado di campionare l'ingresso anche ai fronti di discesa del segnale di clock → la frequenza dati raddoppia e il consumo dinamico si riduce (perché sono necessari metà colpi di clock).

Flip-flop JK

[modifica | modifica sorgente]Il flip-flop JK rende lecita la condizione non permessa J = 1 e K = 1: in questo caso l'uscita Q commuta a ogni colpo di clock invertendo il proprio valore.

| J | K | Q | Q* |

|---|---|---|---|

| 0 | 0 | invariato | invariato |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | invertito | invertito |

Specifiche di temporizzazione

[modifica | modifica sorgente]Le porte NOR introducono ritardi di propagazione → l'uscita commuta sempre dopo un tempo dal comando all'ingresso.

Per garantire il corretto funzionamento di un flip-flop D, al momento del fronte di salita del segnale di clock l'ingresso D dev'essere stabile da un tempo minimo (set-up) e deve rimanere stabile per un tempo minimo (hold). L'uscita commuterà dopo un tempo di propagazione (maggiore del tempo di hold) dal fronte di salita del clock.

Se queste condizioni non vengono rispettate, l'uscita entra in uno stato metastabile di tipo oscillatorio: inizia a commutare indefinitamente tra gli stati logici.

Il resolving time è il tempo entro il quale il flip-flop ritorna in uno stato stabile con una certa probabilità.

La durata minima dei comandi S e R o dell'abilitazione LE è pari a 2 volte il tempo di propagazione .

Occorre inoltre tenere conto dei tempi di transizione del clock: da L a H e da H a L.