Elettronica applicata/Circuiti sequenziali II

Registri

[modifica | modifica sorgente]I segnali numerici possono essere rappresentati e trasferiti in forma seriale o parallela:

- trasferimento seriale:

- vantaggio: una sola linea → minor consumo e costo;

- svantaggio: un bit per volta → più colpi di clock necessari per il trasferimento;

- trasferimento parallelo:

- vantaggio: più bit alla volta → meno colpi di clock necessari per il trasferimento;

- svantaggio: molte linee → maggior consumo e costo.

Registro PIPO (parallelo)

[modifica | modifica sorgente]-

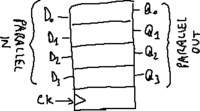

Struttura interna di un registro PIPO a comando sulla transizione

-

Simbolo funzionale di un registro PIPO a comando sulla transizione

Il registro PIPO è in grado di memorizzare un ingresso parallelo su più bit ogniqualvolta viene attivato il segnale di clock/abilitazione; il valore memorizzato viene riportato alle uscite e viene mantenuto costante fino al successivo segnale di clock/abilitazione. Se presente, il segnale di clear permette di resettare a 0 tutti i bit memorizzati. Internamente, il registro PIPO contiene una serie di flip-flop latch D, ciascuno dei quali memorizza uno dei bit della parola in ingresso.

Registro SISO (seriale)

[modifica | modifica sorgente]Il registro SISO è costituito da flip-flop a comando sulla transizione collegati in cascata che condividono lo stesso segnale di clock. A ogni fronte di salita del segnale di clock, il contenuto corrente viene scalato di una posizione: il flip-flop i-esimo passa il bit memorizzato al flip-flop i+1-esimo, quindi riceve il nuovo bit dal flip-flop i−1-esimo, facendo entrare all'estrema sinistra della catena il nuovo bit in ingresso e facendo uscire all'estrema destra l'ultimo bit in eccesso. Registri di questo tipo sono detti registri a scalamento (o shift-register).

Convertitori

[modifica | modifica sorgente]Registro SIPO (seriale-parallelo)

[modifica | modifica sorgente]Nel registro SIPO vengono lette in parallelo le uscite di tutti i singoli flip-flop → è possibile convertire un dato sequenziale in un dato parallelo.

Registro PISO (parallelo-seriale)

[modifica | modifica sorgente]Il registro PISO riceve in parallelo tutti i bit di ingresso, che poi vengono letti a uno a uno in modo seriale. Il segnale di clock innesca solo lo scalamento, mentre il caricamento in parallelo è comandato dal segnale PL.

Contatori

[modifica | modifica sorgente]In un contatore, il valore memorizzato all'interno viene incrementato a ogni segnale di clock. Un contatore modulo 2N (dove N è il numero di bit) ritorna al valore iniziale 0 al 2N-esimo impulso (11...).

Contatori asincroni

[modifica | modifica sorgente]-

Contatore asincrono modulo 4 costituito di flip-flop D

-

Contatore asincrono modulo 4 costituito di flip-flop JK

I contatori asincroni sono costituiti da flip-flop a comando sulla transizione, collegati a catena (ripple) in modo che il segnale di clock di ogni flip-flop è pilotato dall'uscita del flip-flop precedente → il contatore è asincrono perché i flip-flop non sono pilotati dallo stesso segnale di clock.

Esistono due tipi di contatore asincrono:

- flip-flop D: il fronte di salita riporta in uscita il segnale D, che è sempre il complementare dell'uscita → a ogni fronte di salita il flip-flop inverte il proprio valore, e se la nuova uscita è a sua volta un fronte di salita fa commutare anche il flip-flop successivo → si ottiene una sequenza decrescente di numeri binari;

- flip-flop JK: gli ingressi J e K sono sempre a 1 e il clock di ogni flip-flop è negato, quindi a ogni fronte di discesa viene invertito il valore del flip-flop, e se la nuova uscita è a sua volta un fronte di discesa fa commutare anche il flip-flop successivo → si ottiene una sequenza crescente di numeri binari.

Si parla di divisione della frequenza di clock perché il primo flip-flop commuta a ogni impulso di clock, il secondo flip-flop commuta ogni due impulsi di clock, e così via.

Siccome ogni flip-flop ha un ritardo di commutazione, il ritardo complessivo è proporzionale al parallelismo del contatore (numero di flip-flop).

Contatore sincrono

[modifica | modifica sorgente]

In un contatore sincrono tutti i flip-flop condividono lo stesso segnale di clock → tutte le uscite commutano con lo stesso ritardo (in sincronismo).

Il contatore funziona grazie a una serie di porte AND:

- il primo flip-flop commuta a ogni fronte di discesa del segnale di clock (perché gli ingressi J e K sono sempre a 1);

- il secondo flip-flop commuta a ogni fronte di discesa dell'uscita del primo flip-flop;

- il terzo flip-flop commuta quando avvengono in contemporanea il fronte di discesa dell'uscita del primo flip-flop e il fronte di discesa dell'uscita del secondo flip-flop;

- il quarto flip-flop commuta quando avvengono in contemporanea i fronti di discesa di tutti e tre i flip-flop precedenti;

- e così via.

Vincoli di temporizzazione

[modifica | modifica sorgente]La frequenza massima di funzionamento è limitata dai tempi di propagazione del segnale attraverso i circuiti logici combinatori, dai tempi di setup e di hold richiesti per il corretto funzionamento dei flip-flop, e dai tempi di propagazione del segnale attraverso i flip-flop stessi per generare le uscite.

Il terzo flip-flop deve aspettare un ritardo dovuto alla propagazione del segnale attraverso la prima porta logica AND:

Il quarto flip-flop, oltre al ritardo della seconda porta AND, deve anche aspettare il ritardo della prima porta AND la cui uscita è l'ingresso della seconda porta logica AND:

Per evitare l'accumulo del ritardo lungo la catena di flip-flop, è possibile sostituire la struttura a riporto (ripple) con una struttura diretta (look ahead), cioè con una porta AND che non riceva più in ingresso l'uscita di un'altra porta AND:

Macchina a stati finiti

[modifica | modifica sorgente]Una macchina a stati finiti (FSM) è un circuito sequenziale che evolve di stato in stato a ogni colpo di clock. Lo stato futuro dipende sia dagli ingressi correnti, sia dallo stato precedente, che si trova memorizzato nei flip-flop. A ogin stato corrisponde una combinazione delle uscite. La sequenza degli stati è rappresentabile in un diagramma degli stati.